集成电路设计:从概念到实现的完整解析优雅草卓伊凡

一、集成电路设计:芯片制造的”灵魂蓝图”

1.1 什么是集成电路设计?

集成电路(IC)设计是指通过电子设计自动化(EDA)工具,将数百亿晶体管、电阻、电容等元件,按照特定功能需求在微小硅片上排布的过程。其核心产出是:

- 电路原理图(逻辑功能设计)

- 版图(Layout)(物理实现)

- GDSII文件(光刻掩模数据)

设计层级划分:

1.2 IC设计在芯片制造中的作用

| 制造阶段 | 所需设计输入 | 影响权重 |

| 光刻 | GDSII版图 | 50%+ |

| 蚀刻 | 层次化掩模 | 30% |

| 封装 | 引脚分布图 | 20% |

典型案例:

优雅草团队设计的BS.235609765语音识别控制器:

- 采用180nm CMOS工艺

- 集成模拟音频处理+数字逻辑单元

- 功耗<10mW,误唤醒率<0.1次/天

二、两个比喻理解IC设计

比喻1:IC设计如城市规划

- 晶体管=建筑物

- 互连线=道路管网

- 时钟树=公共交通系统

- 功耗优化=能源分配方案

糟糕设计的后果:

若”道路”(金属连线)太窄,会导致:

- “堵车”(信号延迟)

- “车祸”(信号串扰)

比喻2:IC设计像编写交响乐

- 功能模块=乐器组

- 时序约束=节拍器

- 信号完整性=音准协调

- 低功耗模式=弱音踏板

正如优雅草杜江所说:

“好的IC设计要让每个’音符’(晶体管)在正确的时间发声,同时避免’杂音’(噪声干扰)”

三、优雅草的IC设计实践

3.1 BS.235609765芯片设计揭秘

技术亮点:

- 混合信号设计:

-

- 模拟部分:麦克风前置放大器(信噪比>65dB)

- 数字部分:CNN加速器(0.8TOPS/W)

- 低功耗技术:

-

- 多电压域设计

- 时钟门控覆盖率>90%

团队分工:

| 成员 | 职责 | 创新贡献 |

|———|———|—————|

| 杜江 | 系统架构 | 语音激活算法硬件化 |

| 卢健 | 模拟电路 | 高精度ADC设计 |

| 吴银满 | 数字后端 | 时序收敛优化 |

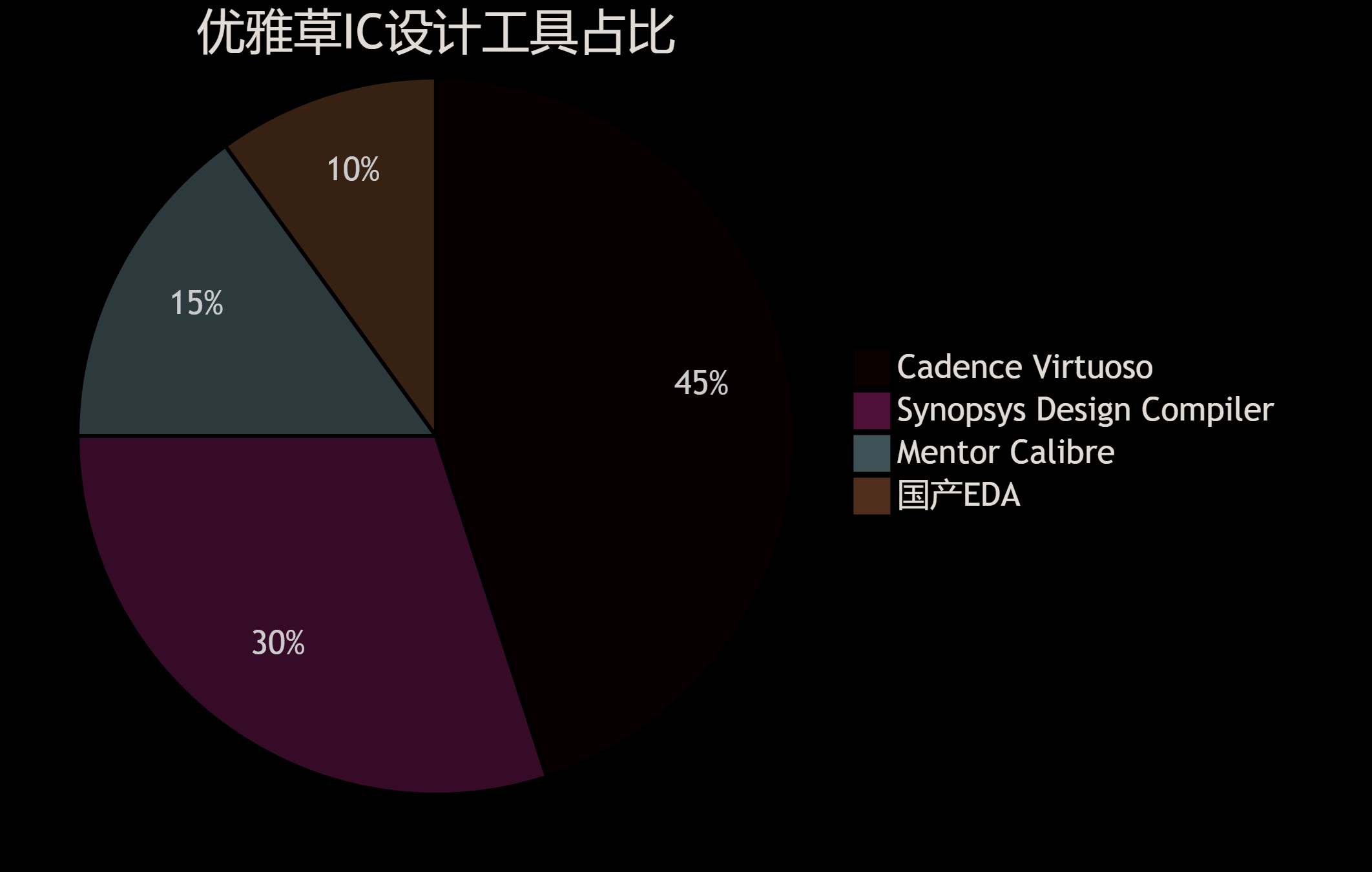

3.2 开发环境准备

硬件需求:

- 工作站配置:

-

- CPU:AMD EPYC 32核以上

- GPU:NVIDIA A100(用于物理验证加速)

- 内存:256GB+(大型设计占用)

软件工具链:

四、IC设计全流程解析

4.1 前端设计阶段

- 需求分析:

-

- 制定SPEC(如BS.235609765的唤醒词识别率≥98%)

- RTL编码:

module wake_detector(input clk,input [15:0] audio_in,output reg wake_signal

);// 卷积神经网络实现always @(posedge clk) beginif (cnn_out > THRESHOLD) wake_signal <= 1'b1;end

endmodule- 功能仿真:

-

- 使用UVM验证框架

- 覆盖率要求>95%

4.2 后端实现阶段

关键步骤:

- 逻辑综合:将RTL转为门级网表

- 布局布线:

-

- 标准单元摆放

- 时钟树综合(CTS)

- 物理验证:

-

- DRC(设计规则检查)

- LVS(版图vs原理图一致性)

挑战案例:

在BS.235609765开发中,曾因天线效应导致良率下降30%,最终通过:

- 增加跳线层

- 优化金属填充模式

解决问题

五、集成电路布图设计专利指南

5.1 专利申请四要素

- 新颖性:区别于现有设计(如优雅草的噪声抑制结构)

- 创造性:非显而易见(如混合信号布局方法)

- 实用性:可工业化生产

- 充分公开:提供足够实施细节

5.2 优雅草即将发布的专题

《从布图到专利》系列大纲:

- 前期准备:

-

- 专利检索策略

- 技术交底书撰写

- 设计阶段:

-

- 独创性特征标注

- 规避现有专利

- 申请实战:

-

- 权利要求书撰写技巧

- 审查意见答复策略

示例片段:

“在版图设计中,我们采用’蛇形走线+屏蔽层’的组合(附图3),将串扰降低12dB,这将成为权利要求1的核心特征…”

六、给初学者的建议

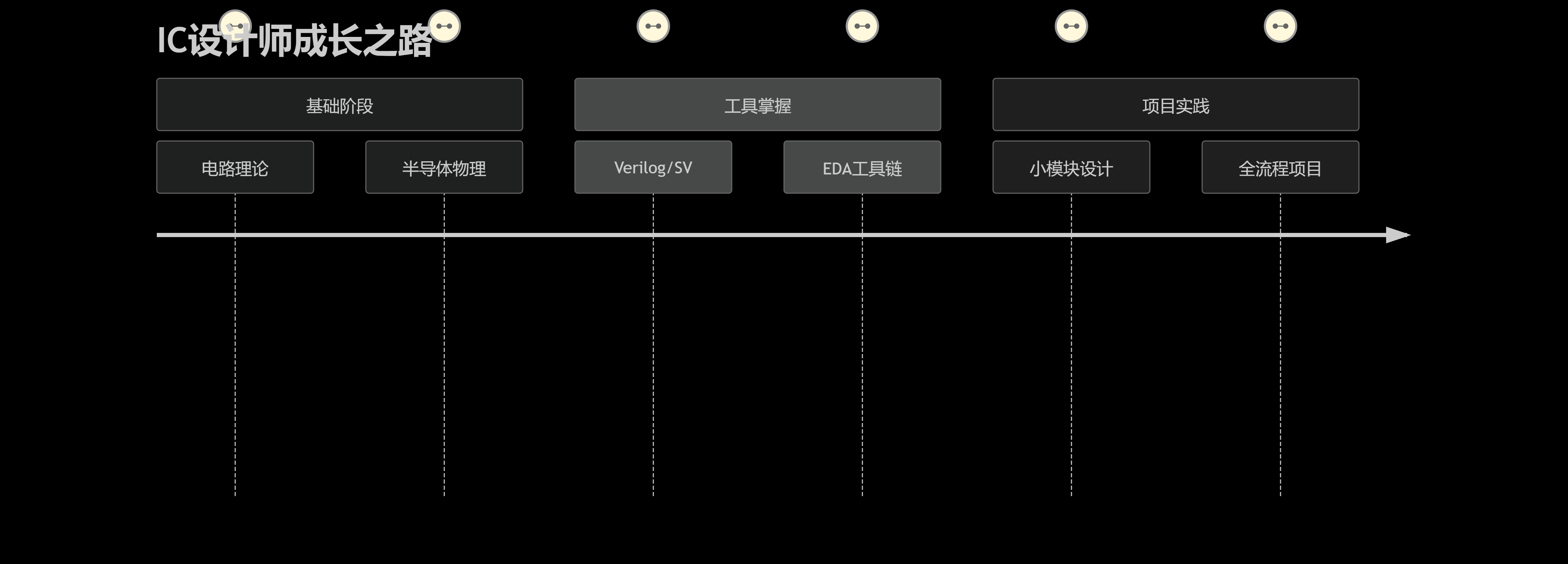

6.1 学习路径

6.2 推荐资源

- 教材:

-

- 《CMOS VLSI Design》 Neil Weste

- 《专用集成电路设计》 虞希清

- 开源项目:

-

- RISC-V开源SoC(如Efabless项目)

- SkyWater 130nm PDK

结语:中国IC设计的未来在脚下

优雅草科技从智能家电控制芯片起步,未来规划目标:

- 2024年:完成55nm语音AI芯片流片

- 2025年:建立混合信号IP库

- 2026年:参与RISC-V生态建设

正如卓伊凡在博客中写道:

“每个焊点都是星辰大海的起点,我们发布的不仅是BS.235609765芯片,更是国产IC设计的火种。”

敬请关注:

- 卓伊凡博客集成电路专栏(更新频率:双周更)