有符号数负数补码相加时,全部位都参与运算,包括符号位,当相加和超出定义位宽时自动丢掉高位。

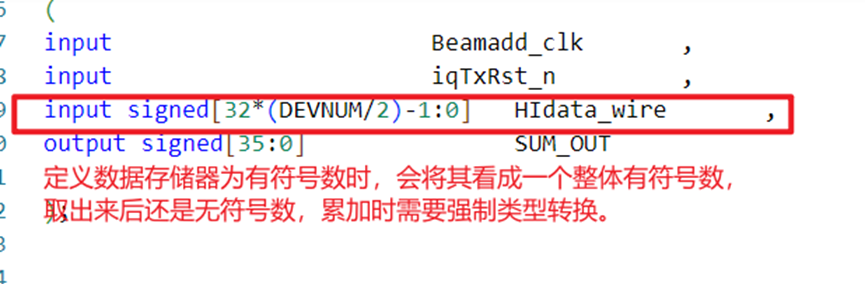

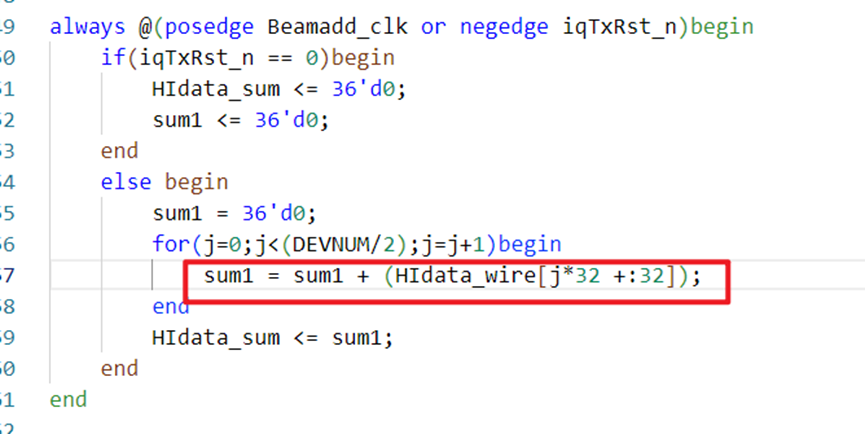

出现问题原因分析:

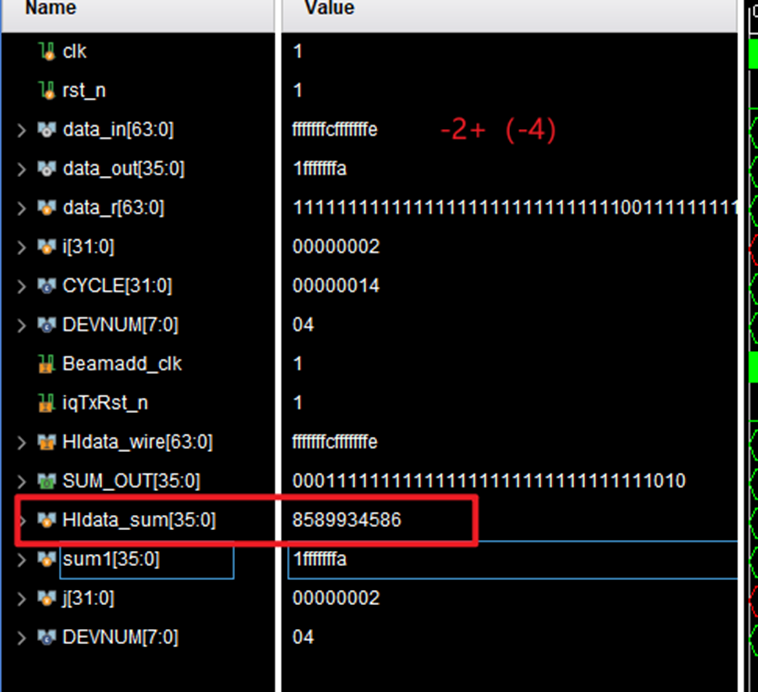

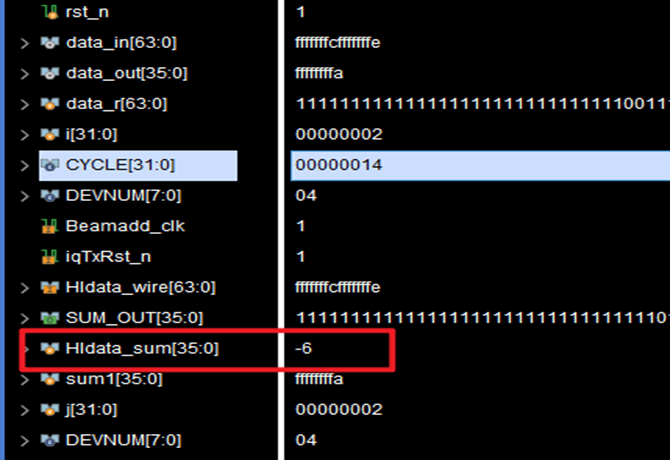

虽然输入数据HIdata_wire[32*(DEVMUM/2)-1:0]定义为有符号数,但其内部不是一个数据,相当于串行数据存储器,因此会将其整体看成一个有符号数,当累加时取出的数据依然是按默认无符号来对待,导致数据出错。(按无符号数相加了)

-2的补码:2^32-2=4294967296-2=4294967294

-4的补码:2^32-4=4294967292

4294967294 + 4294967292=8,589,934,586

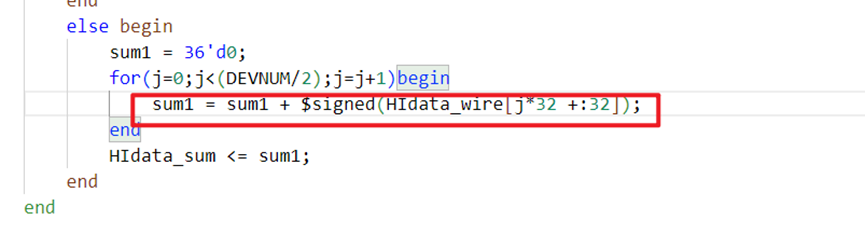

解决办法:

累加前进行强制类型转换为有符号数

计算结果正确。

注意:①当数据被认为是无符号数时,补码所有位直接相加,也就是按正数相加。

②当被认为是负数时,会自动匹配出符合数值的数据位宽,然后相加求和舍弃后再进行符号 位的扩展。(扩展的符号位不参与运算)。自己解释的

③VHDL强制类型转换为 TO_SIGNED(-5,8)。