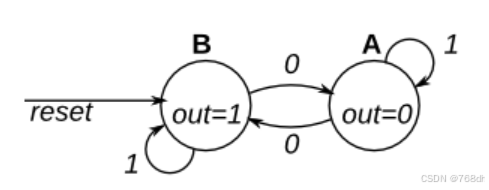

This is a Moore state machine with two states, one input, and one output. Implement this state machine. Notice that the reset state is B.

This exercise is the same as fsm1, but using synchronous reset.

一段式写法:

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);input clk;input reset; // Synchronous reset to state Binput in;output out;// reg out;// Fill in state name declarationsparameter A=0, B=1; reg present_state, next_state;always @(posedge clk) beginif (reset) begin // Fill in reset logicpresent_state <= B;out <= 1;end else begincase (present_state)// Fill in state transition logicA : next_state = in? A:B;B : next_state = in? B:A;endcase// State flip-flopspresent_state = next_state; case (present_state)// Fill in output logicA: out <= 0;B: out <= 1;endcaseendendendmodule

三段式

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);input clk;input reset; // Synchronous reset to state Binput in;output out;// reg out;// Fill in state name declarationsparameter A=0, B=1; reg present_state, next_state;//三段式//--状态机第一段:同步时序描述状态转移always @(posedge clk)beginif(reset)present_state <= B; //复位初始状态elsepresent_state <= next_state; //次态转移到现态end//--状态机第二段:组合逻辑判断状态转移条件,描述状态转移规律always @(*)begin //任意变量变化case(present_state)A : next_state = in? A:B;B : next_state = in? B:A;endcaseend//--状态机第三段:时序逻辑描述输出/* always @(posedge clk)beginif(reset)out<= 1;else begincase(next_state) //根据下一状态进行输出A: out <= 0;B: out <= 1;default : out <= 0;endcaseendend*/assign out = (present_state==B);//根据上一个状态进行输出

endmodule两段式

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);input clk;input reset; // Synchronous reset to state Binput in;output out;// reg out;// Fill in state name declarationsparameter A=0, B=1; reg present_state, next_state;//两段式//--状态机第一段:同步时序描述状态转移always @(posedge clk)beginif(reset)present_state <= B; //复位初始状态elsepresent_state <= next_state; //次态转移到现态end//--状态机第二段:组合逻辑判断状态转移条件,描述状态转移规律以及输出always @(*)begincase(present_state)A : beginout = 0;next_state = in? A:B;endB : beginout = 1;next_state = in? B:A;endendcaseend

endmodule

问题总结:

1、三段式 和两段式书写中 状态机第二段 需要写 always@(*)

2、三段式书写过程中,第三段 本题既可以按组合逻辑赋值也可以按时序逻辑赋值,但在使用时序逻辑赋值的时候,注意case 中的条件为次态(next_state)。当为present_state时。结果如下

从图中可以看出,输出晚了1拍,假设in从1—>0时状态从A->B,根据第二段组合逻辑判断状态转移 next_state立刻变成了 B。根据第一段 同步时序描述状态转移,则在下一个上升沿到来时 present_state 变为 B。如果case中写pre的话就会晚一个时钟周期。而采用组合逻辑正好。