工艺流程要求及可测试性要求

- 1.工艺流程要求

- 2.可测试性要求

1.工艺流程要求

BOTTOM 面表贴器件需过波峰时,应确定贴装阻容件与 SOP 的布局方向正确,SOP 器件轴向需与波峰方向一致。

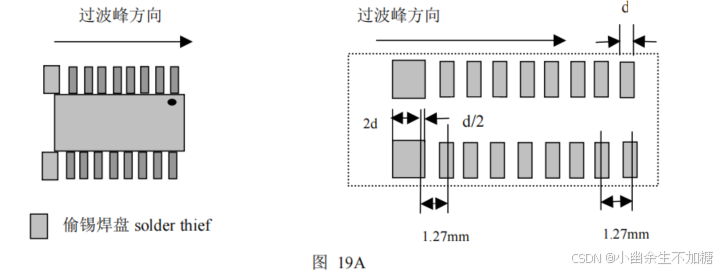

SOP 器件在过波峰尾端需接增加一对偷锡盘。尺寸满足图 19 要求。

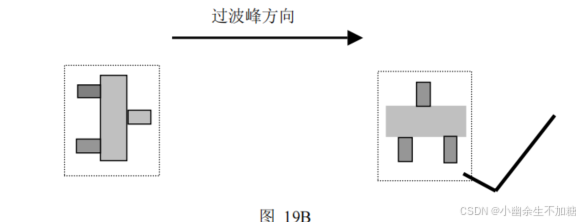

b.SOT 器件过波峰尽量满足最佳方向。

片式全端子器件(电阻、电容)对过波峰方向不作特别要求。

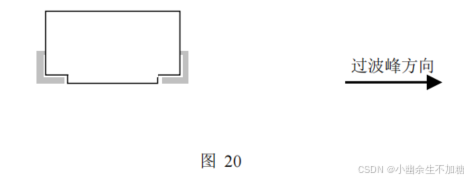

d.片式非全端子器件(钽电容、二极管)过波峰最佳时方向需满足轴向与进板方向平行。(图20)

SOJ、PLCC、QFP 等表贴器件不能过波峰焊。

过波峰焊的 SOP 之 PIN 间距大于 1.0mm,片式元件在 0603 以上。

2.可测试性要求

是否采用测试点测试。如果制成板不采用测试点进行测试,对下列项不作要求PCB 上应有两个以上的定位孔(定位孔不能为腰形)。

定位的尺寸应符合直径为(3~5cm)要求

定位孔位置在 PCB 上应不对称

应有有符合规范的工艺边

对长或宽>200mm 的制成板应留有符合规范的压低杆点

需测试器件管脚间距应是 2.54mm 的倍数

不能将 SMT 元件的焊盘作为测试点

测试点的位置都应在焊接面上(二次电源该项不作要求)

测试点的形状、大小应符合规范

测试点建议选择方形焊盘(选圆形亦可接受),焊盘尺寸不能小于 1mm*mm

测试点应都有标注(以 TP1、TP2…进行标注)

所有测试点都应已固化(PCB 上改测试点时必须修改属性才能移动位置)

测试的间距应大于 2.54mm

测试点与焊接面上的元件的间距应大于 2.54mm

低压测试点和高压测试点的间距离应符合安规要求

测试点到 PCB 板边缘的距离应大于 125mil/3.175mm

测试点到定位孔的距离应该大于 0.5mm,为定位柱提供一定净空间

测试点的密度不能大于每平方厘米 4-5 个,测试点需均匀分布

电源和地的测试点要求。每根测试针最大可承受 2A 电流,每增加 2A,对电源和地都要求多提供一个测试点对于数字逻辑单板,一般每5个I℃应提供一个地线测试点。焊接面元器件高度不能超过 150mil/3.81mm,若超过此值,应把超高器件列表通知装备工程师,以便特殊处理

接插件管脚的间距应是 2.54mm 的倍数

所有的测试点应都已引至接插件上

应使用可调器件

对于 ICT 测试,每个节点都要有测试,对于功能测试,调整点、接地点、交流输入、放电电容、需要测试的表贴器件等要有测试点。

测试点不能被条形码等挡住,不能被胶等覆盖。

如果单板需要喷涂”三防漆”,测试焊盘必须进行特殊处理,以避免影响探针可靠接触。

)