-

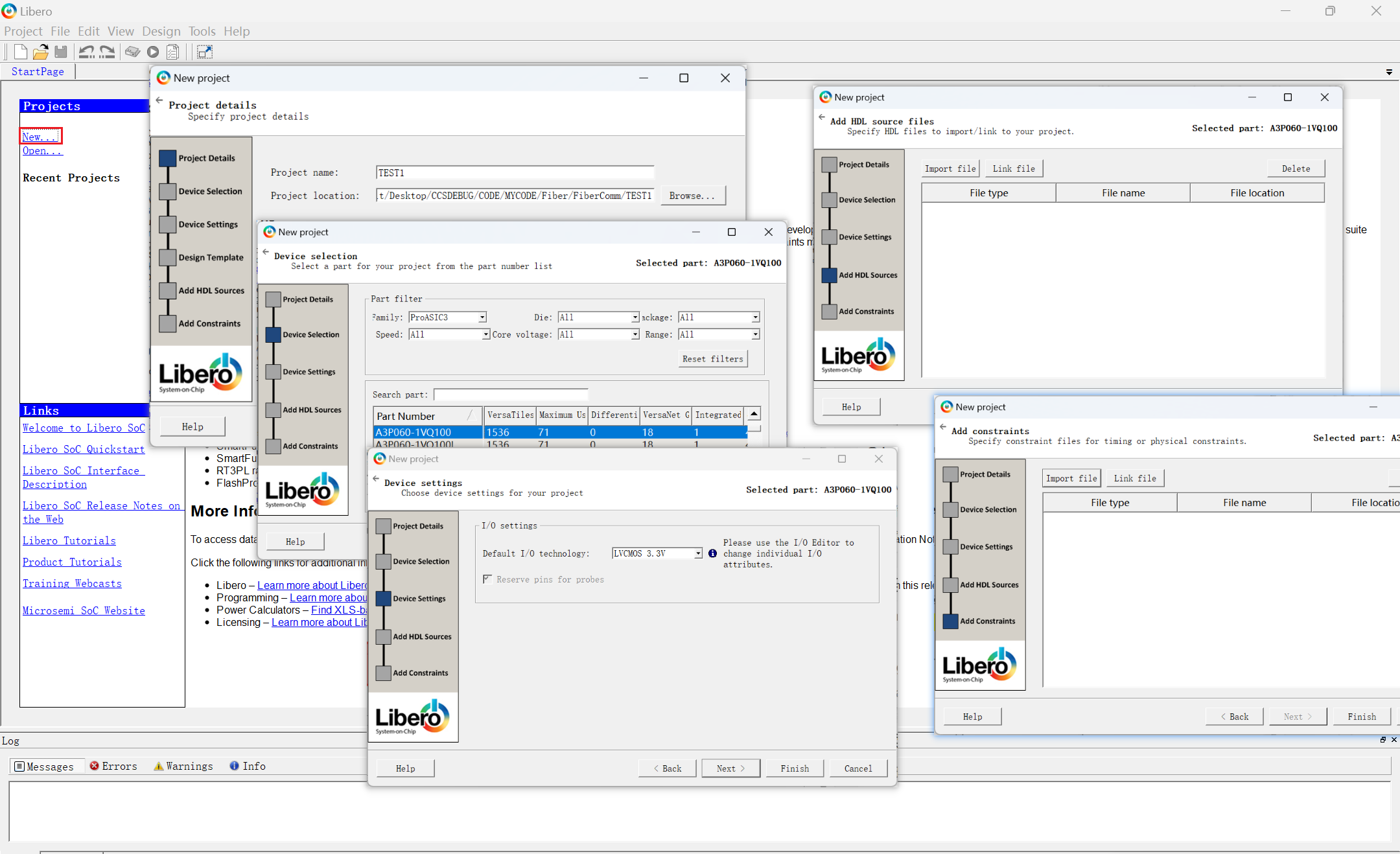

新建项目

-

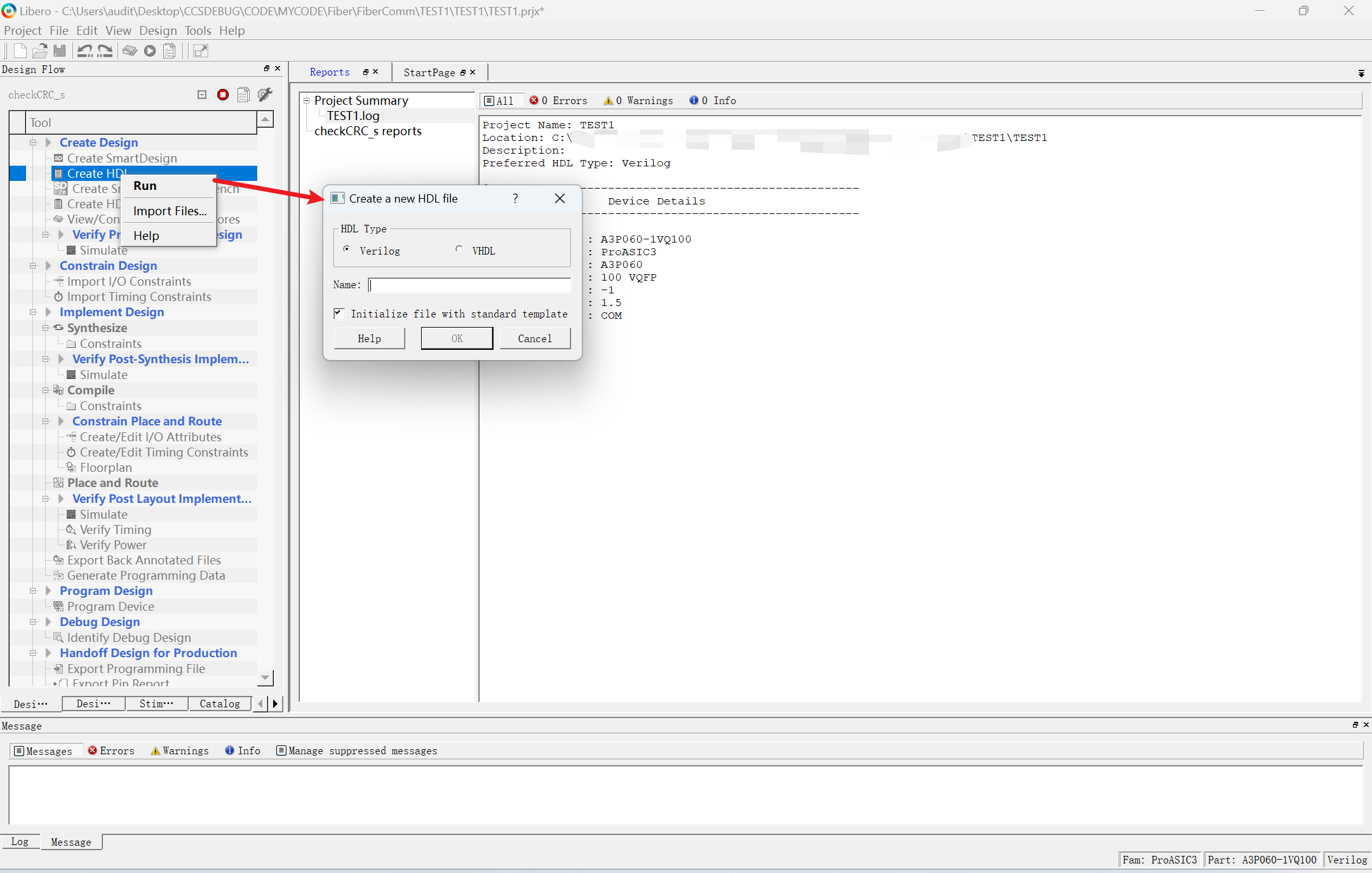

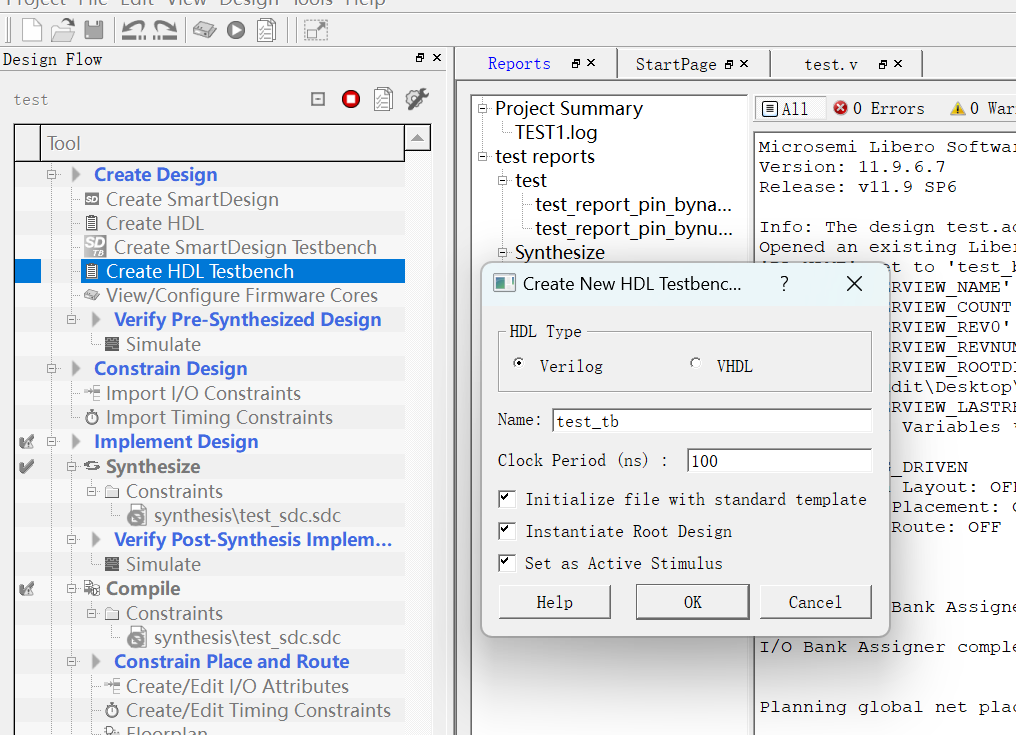

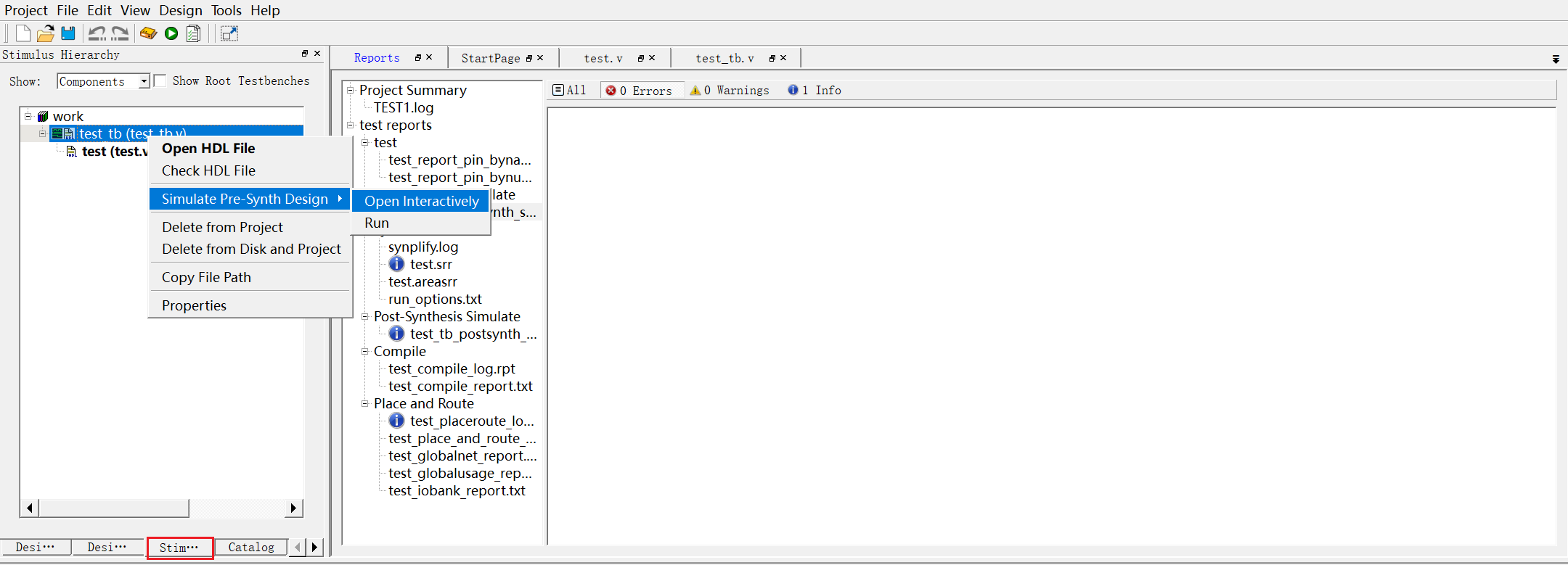

项目初始界面中创建或导入设计文件:

-

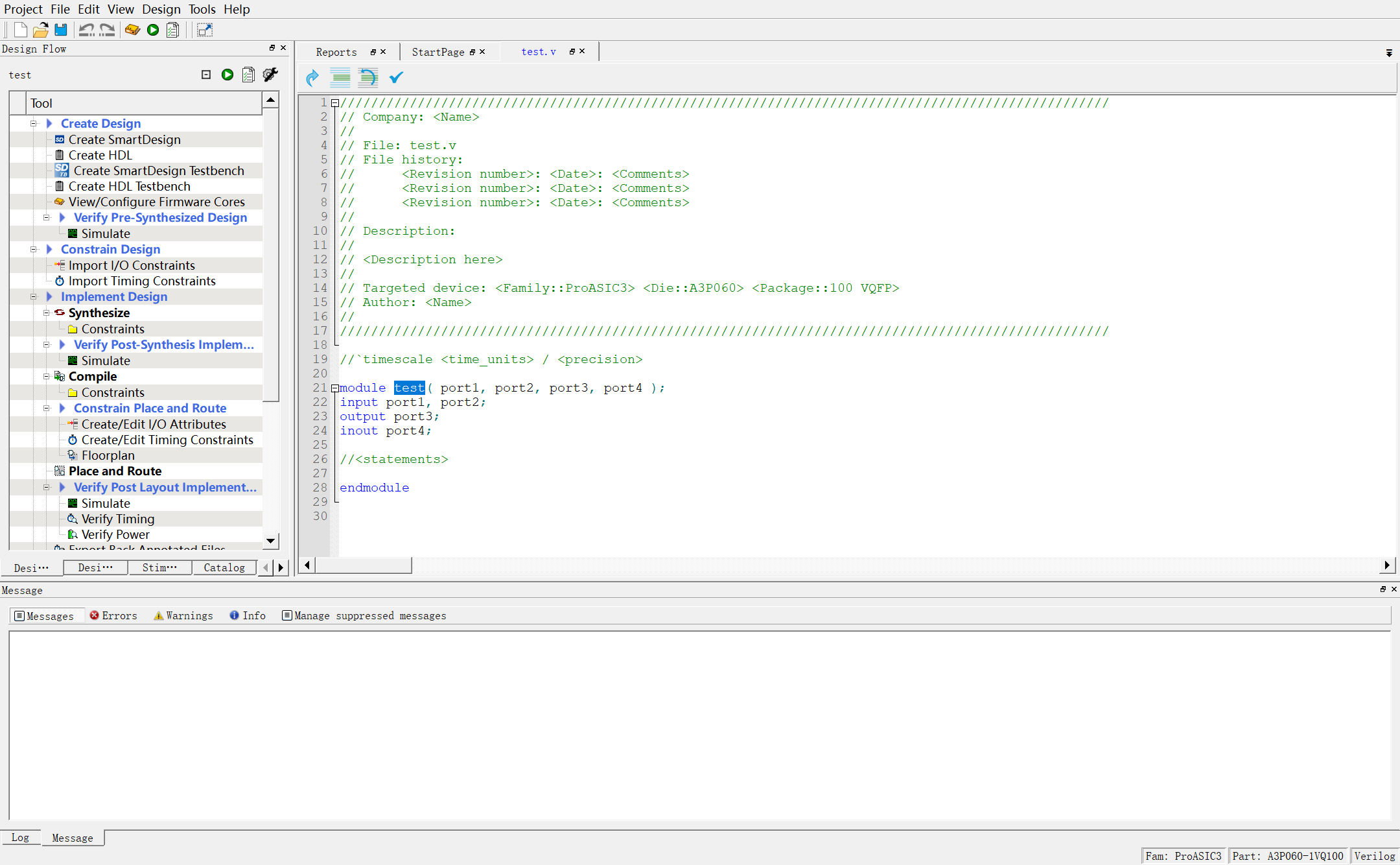

新建HDL文件

module test (input [3:0] a,input [3:0] b,output reg [3:0] sum,output reg carry_out

);always @(*) begin{carry_out, sum} = a + b;

endendmodule

-

点击此按钮可进行项目信息的重新配置:

-

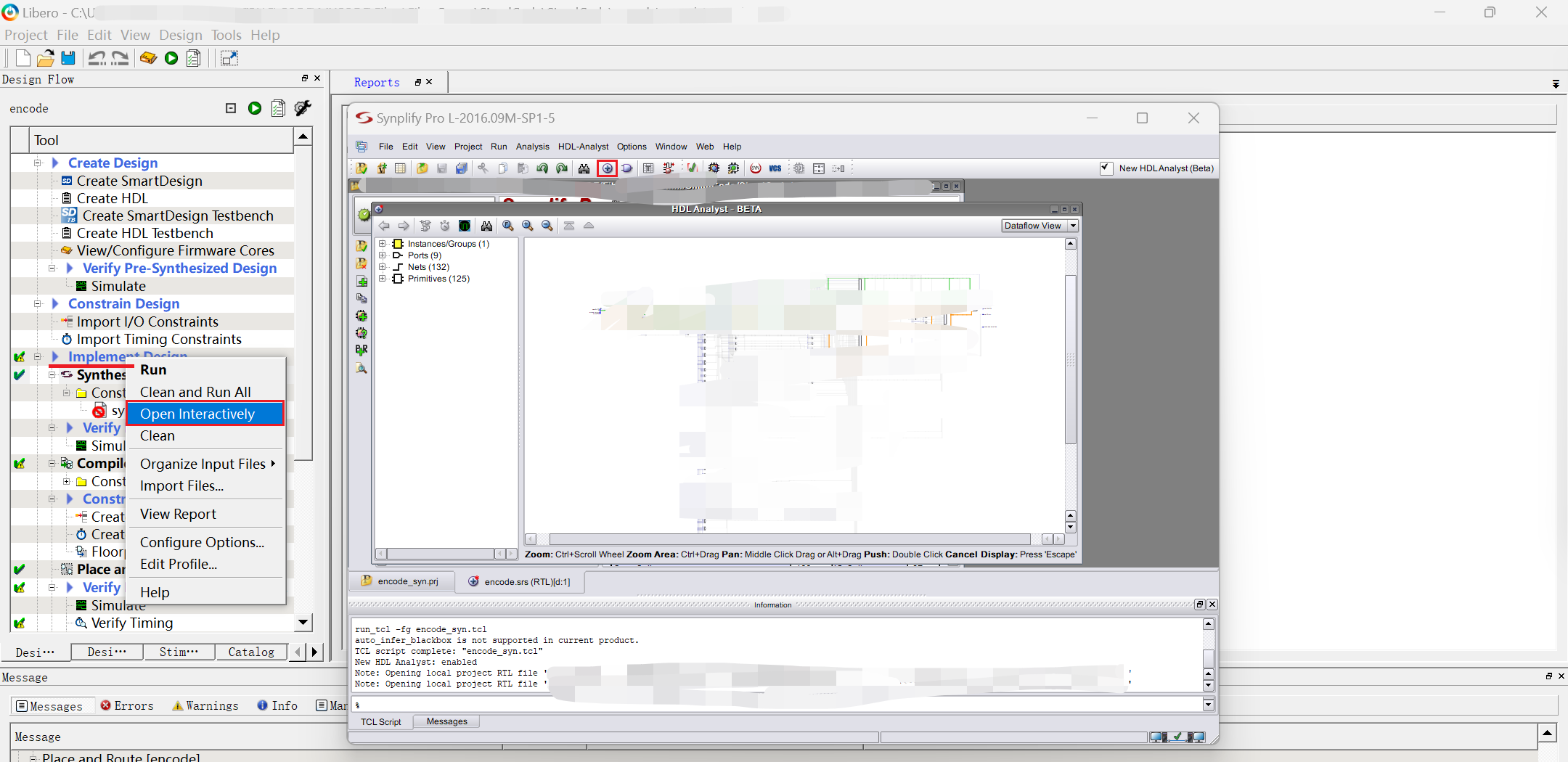

综合:

-

Libero Soc RTL Viewer

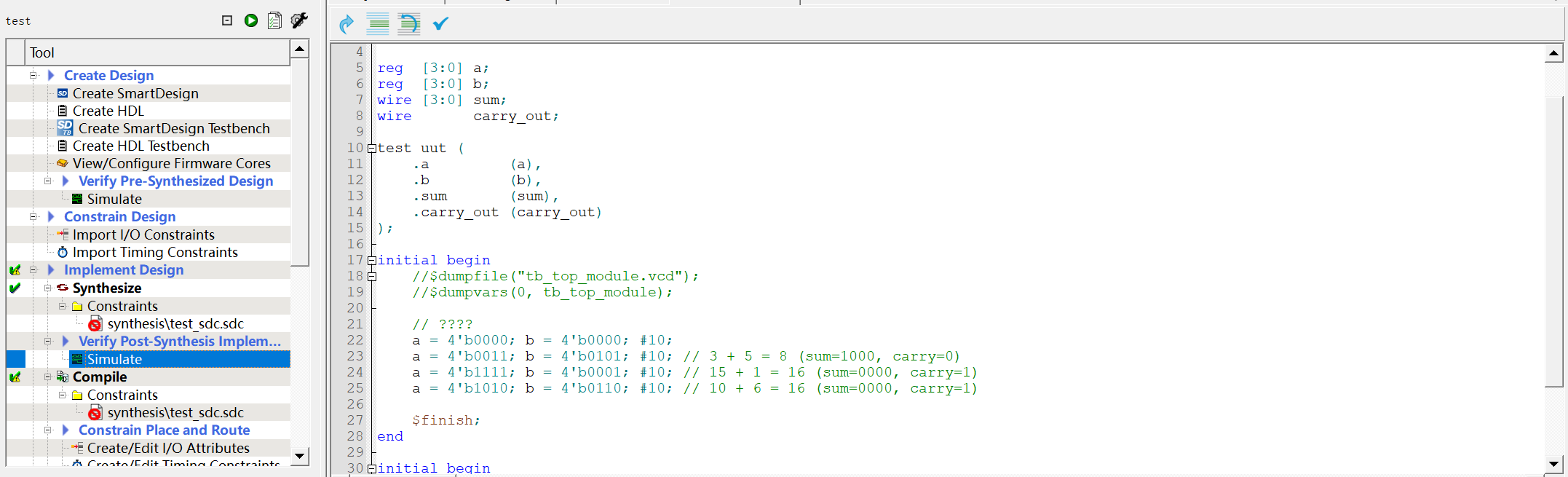

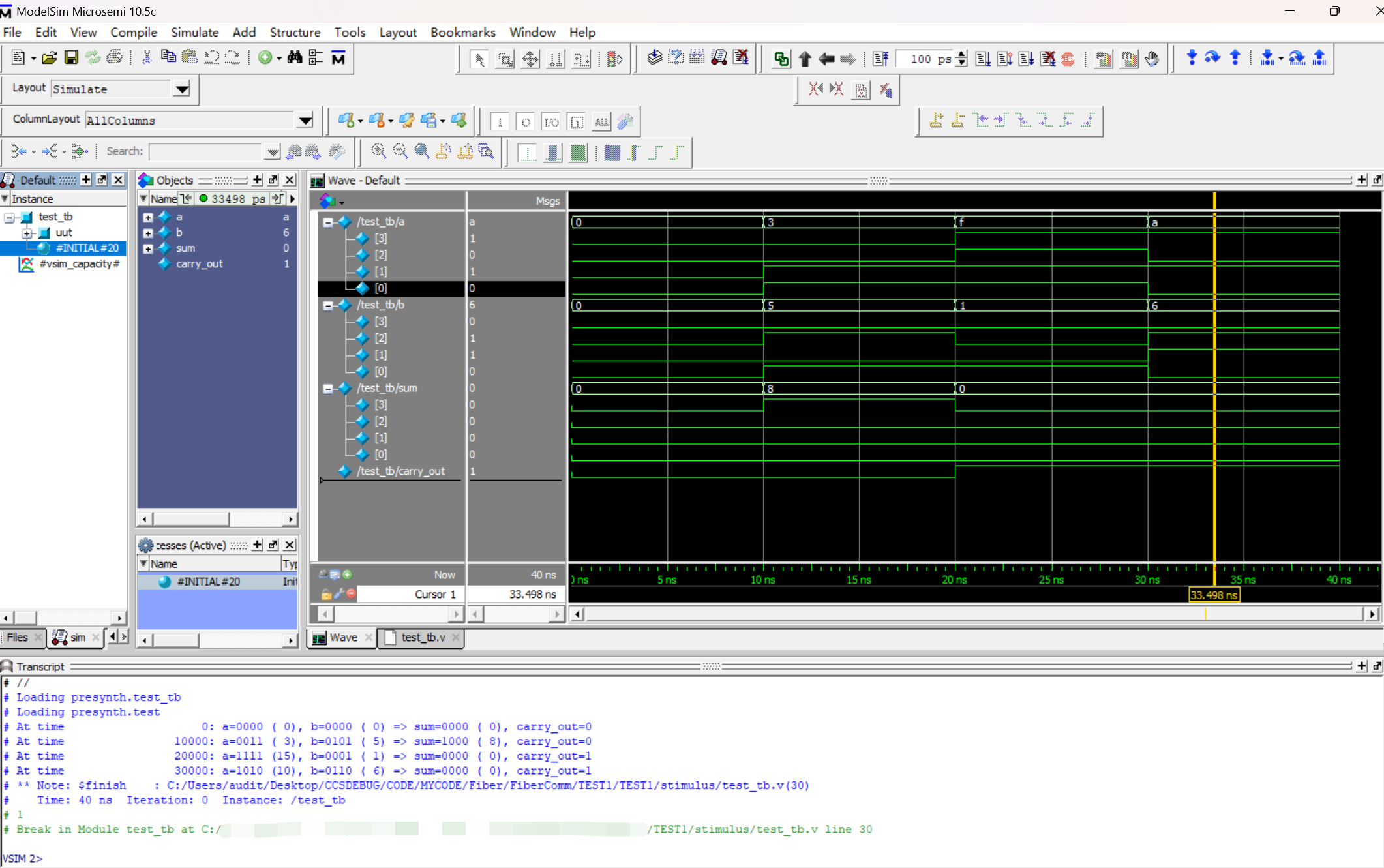

`timescale 1 ns / 1 psmodule test_tb;reg [3:0] a;

reg [3:0] b;

wire [3:0] sum;

wire carry_out;test uut (.a (a),.b (b),.sum (sum),.carry_out (carry_out)

);initial begina = 4'b0000; b = 4'b0000; #10;a = 4'b0011; b = 4'b0101; #10; // 3 + 5 = 8 (sum=1000, carry=0)a = 4'b1111; b = 4'b0001; #10; // 15 + 1 = 16 (sum=0000, carry=1)a = 4'b1010; b = 4'b0110; #10; // 10 + 6 = 16 (sum=0000, carry=1)$finish;

endinitial begin$monitor("At time %t: a=%b (%d), b=%b (%d) => sum=%b (%d), carry_out=%b",$time, a, a, b, b, sum, sum, carry_out);

endendmodule

- 或者

全生态接入系统技术白皮书)