-

时钟

- 定义

周期型的0、1信号

时钟信号由“心脏”时钟源产生,通过“动脉”时钟树传播到整个芯片中。

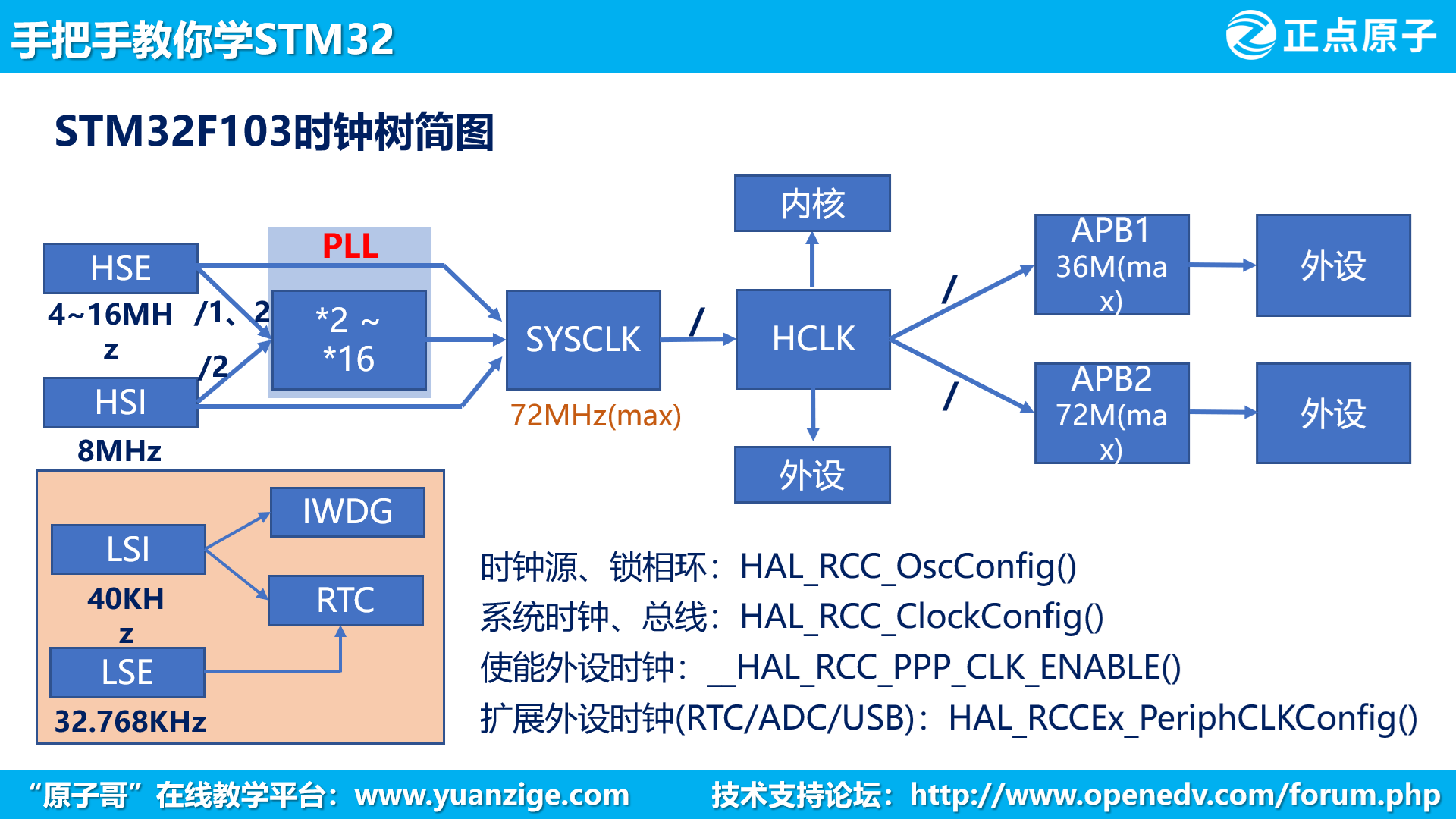

SYSCLK系统时钟,由HSI、HSE、PLLCLK三选一。

HCLK是AHB总线时钟, PCLK是APB总线时钟。

使用某个外设,必须要先使能该外设时钟 - 系统时钟配置

- 作用

- 实现芯片里电路同步。 寄存器在时钟上升沿时,把最终运算结果写入寄存器,即把寄存器输入端(值稳定)传给输出端。串口需要固定的波特率通信,IIC需要时钟线。

- 决定数字电路的运行速度

- 时钟源

- 晶振(HSE高速外部时钟),使用PLL(锁相环)倍频

- RC 振荡电路(HSI高速内部时钟),精度相对较差

- 定义

-

寄存器

寄存器是特殊的存储器,可以实现对单片机各个功能的控制。寄存器就是单片机内部的控制机构。 -

APB总线协议

APB 看成一种“线”,这种线是来连接两个设备,一个是master,一个是slave,所有数据传输都是master来控制,slave来回应。

数据传输在PCLK时钟上升沿进行

进行一次数据传输至少需要两个时钟周期 -

UART总线协议

通信过程:

交叉连接两台设备的TXD、RXD

配置两台设备的波特率、停止位、奇偶校验位,保持一致

发送数据,从起始位到结束位,整个数据包以串行的方式,从发送设备端送至接收设备端

接受端以预配置的波特率 对数据线进行采样,

接收设备采样的数据,首先会丢弃数据帧中的起始位、奇偶检验位和停止位,剩下的是有效数据位

全双工通信

缺点:异步通信*(无时钟线),和UDP类似,无法确保接收端收到数据 -

I2C总线协议

使用示波器和逻辑分析仪调试

用示波器观察总线上的波形是否有畸变

用逻辑分析仪做数据解析。

半双工通信 -

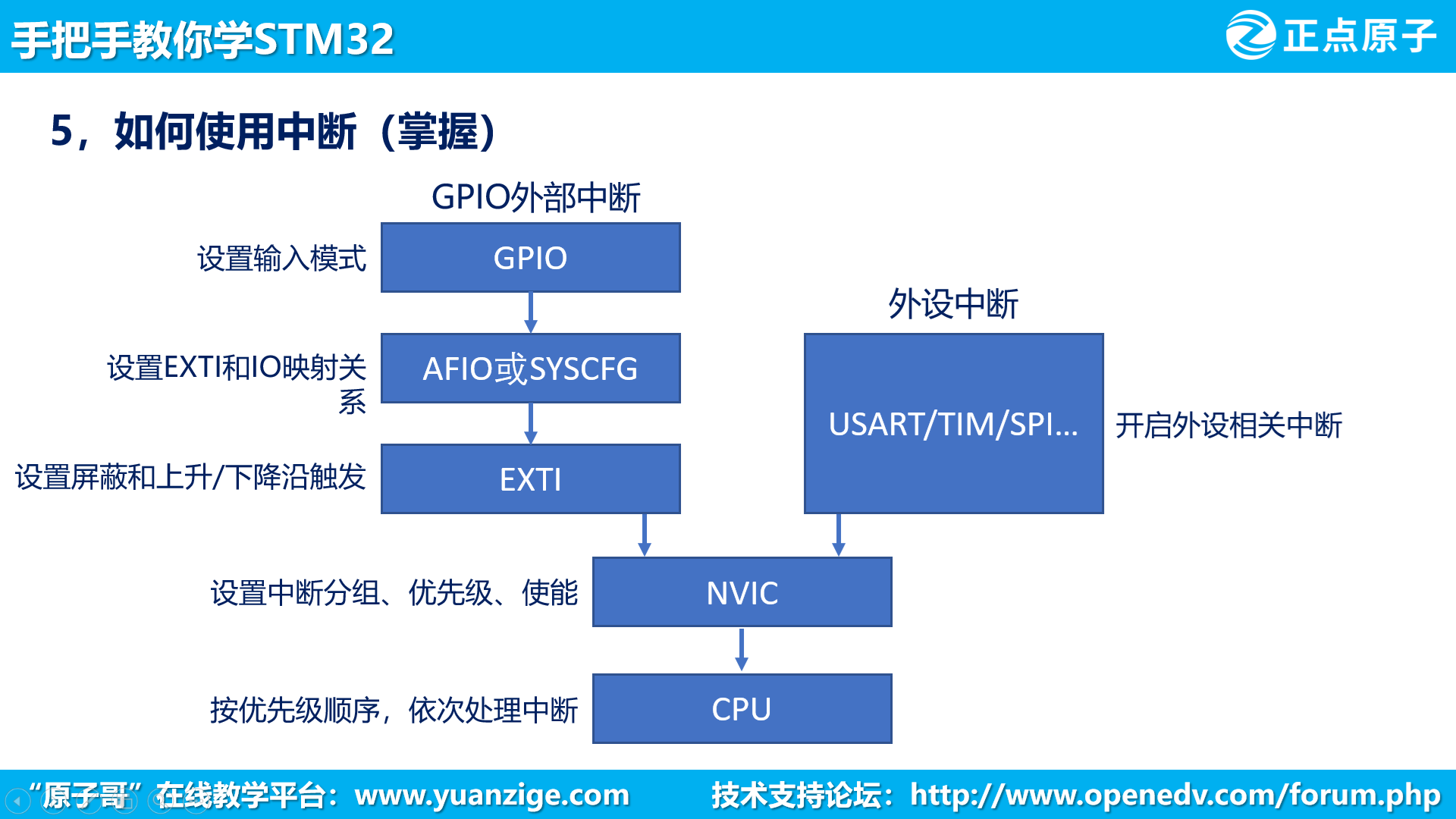

中断

- NVIC相关寄存器:

- 中断使能寄存器,打开中断,每个位对应一个外部中断

- 中断除能寄存器,关闭中断,每个位对应一个外部中断

- EXTI相关寄存器

- 中断屏蔽寄存器,位值为0表示屏蔽相应线上的中断请求,位值为1表示开放相应线上的中断请求

清除 - 请求挂起寄存器, 状态标记,可以用来清除状态。位值为0表示相应线上没有触发中断请求,位值为1表示相应线上触发请求。在中断处理函数中可以通过写入位值1来清除中断标记,把相应值变成0。

- 中断屏蔽寄存器,位值为0表示屏蔽相应线上的中断请求,位值为1表示开放相应线上的中断请求

- 使用中断

- NVIC相关寄存器:

-

音频codec芯片

Soc使用I2C协议读写codec芯片的寄存器,来配置codec芯片。 使用I2S协议传输音频数据。

播放时,DMA的方向是内存到外设, 目的地址是I2S的数据寄存器,然后使用I2S协议把音频数据发送到codec芯片

嵌入式驱动学习

2025/11/9 11:46:50

来源:https://blog.csdn.net/qq_28808697/article/details/147642055

浏览:

次

关键词:嵌入式驱动学习

版权声明:

本网仅为发布的内容提供存储空间,不对发表、转载的内容提供任何形式的保证。凡本网注明“来源:XXX网络”的作品,均转载自其它媒体,著作权归作者所有,商业转载请联系作者获得授权,非商业转载请注明出处。

我们尊重并感谢每一位作者,均已注明文章来源和作者。如因作品内容、版权或其它问题,请及时与我们联系,联系邮箱:809451989@qq.com,投稿邮箱:809451989@qq.com

)

)