注:内容大部分翻译来源:mindshare chapter 12;

在链路训练时,pcie 永远都会从gen1开始进行;在gen1 速率到达L0状态时,若此时capability中设置的max speed不是gen1则会进入到recovery状态接着跳到genX中。其中TS1 中symbol 4的bit7 speed_change一定会被置起。在recovery.rcvrlock 状态。

其中当gen5时有两个选项可以加快traning:

1. equalization bypass to highest rate:链路在gen1 L0时可以直接进行Gen5(highest rate)的训练,不需要经过gen3,gen4;

2. No equaliztion needed: 当支持时,从gen5降到gen4或gen3时不需要从新进行eq训练。

Gen3主要改变:新的编码方式,以及复杂的eq训练(sophisticated signal equalization mode)

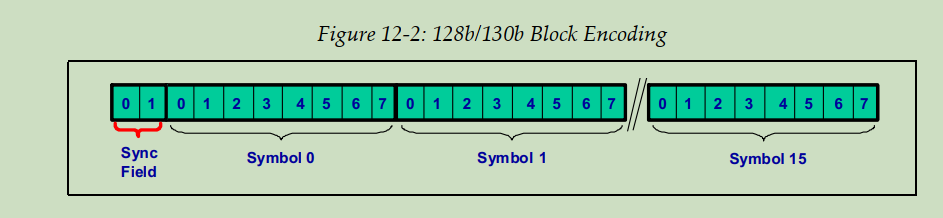

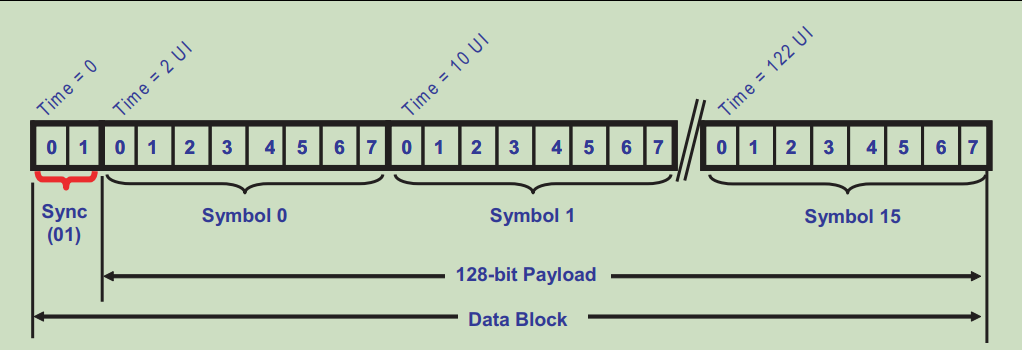

128b/130b 编码

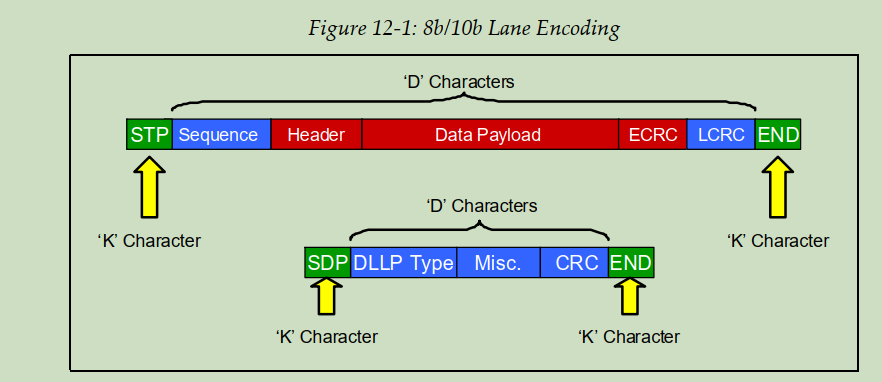

8b/10b:对齐K码的方式进行编码和解码;

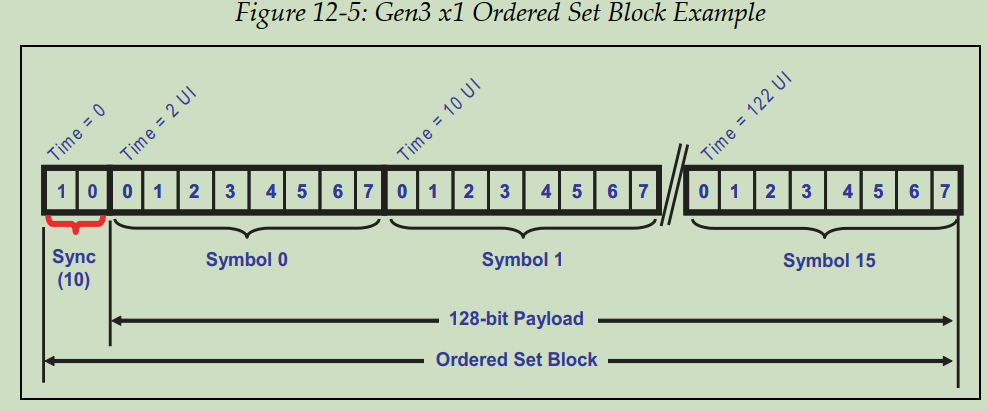

新的编码方式以16B为一组。每个通道看到的还是8bit码流。

sync file用于表示是data还是order set;rx端如果是order set的话必须在所有通道上同时传输。

复杂信号的均衡

相比于gen1,gen2 固定的de-emphasis;gen3 可以动态调整(present)

8Gbps,编码

低位先发送;

block alignment

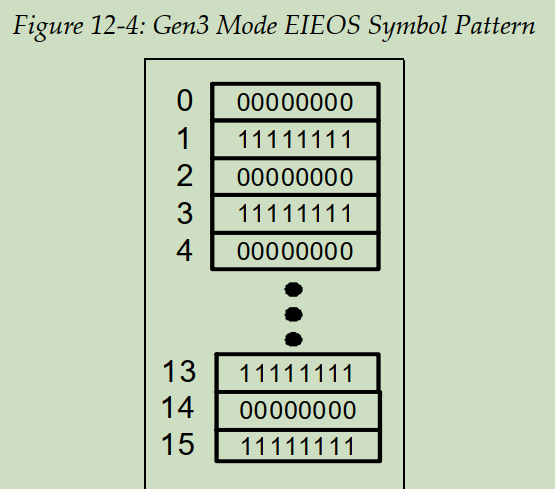

通过发送EIOS(electric order set)来进行块的锁定。

order set block

注:gen1,gen2,gen3中都称为order set ;但是gen1,gen2 是10bit格式,用K码来表示;gen3中是每个ordered set16个symbol;

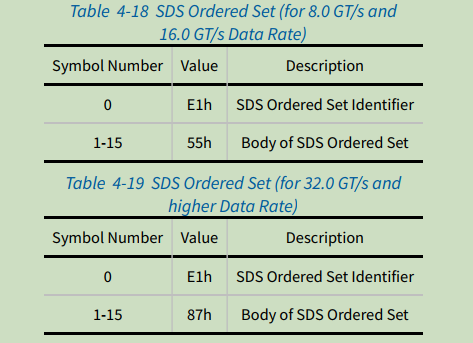

gen3 ordered set共有以下几种:

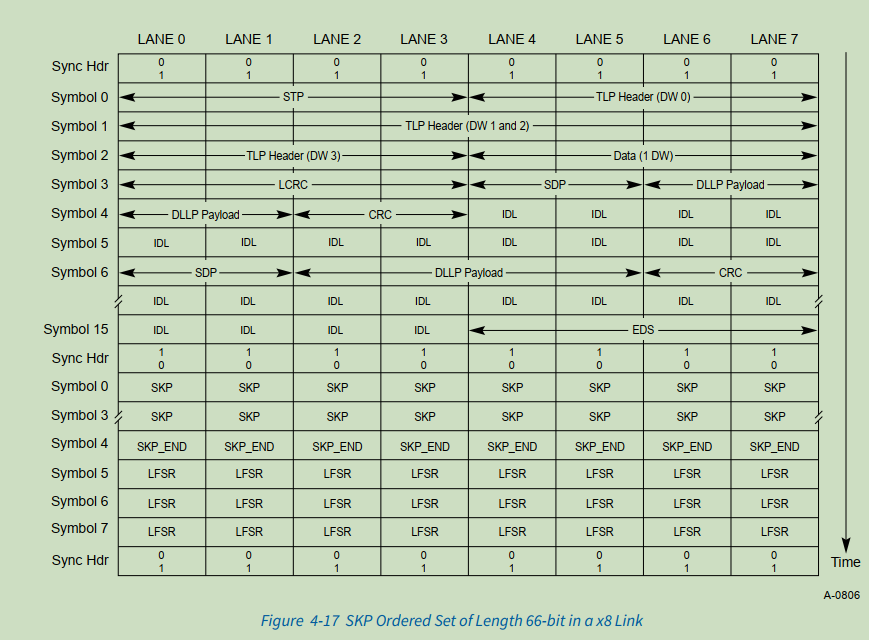

1.SOS,skip ordered set;用于时钟补偿;

2. EIOS- electrical idle ordered set;用来进入 electrical idle state;

3. EIOS,退出elecidle ;gen3 下block对齐。

4. TS1,

5 TS2,

6. FTS :用于退出L0s(NFTS)

ordered set 在所有lane上必须同时出现(rx,tx lane)

这个长度规则的一个例外是 SOS(SKP 有序集),它允许由时钟补偿逻辑(例如与链路中继器相关的逻辑)以每组四个 SKP 符号的方式添加或移除。因此,SOS 的合法长度可以是 8、12、16、20 或 24 字节。

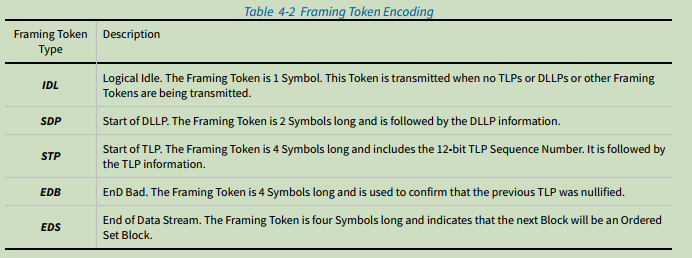

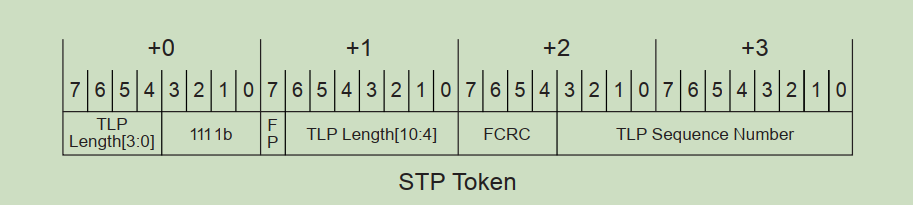

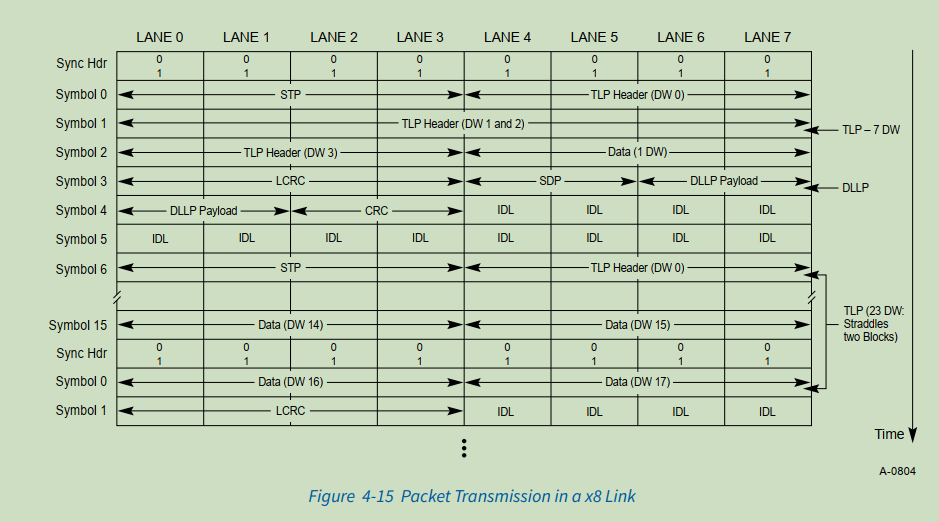

Five types of Data structures (called Framing Tokens) are also used within a Data Block.五种数据类型的结构成为信令(tokens)。STP,SDP,IDLE,EDS,EDB;

data+skp ordered set fram;

(此处mindshare 的gen3 fram 和spec有出入,以gen5 spec为主)

一旦两个端口都进入 Recovery 状态,从进入到完成整个恢复的往返时间预计不超过 1 微秒(1µs)。

TX 编码规则:

STP之后紧跟这tlp包内容。如果是nullified 数据包(结尾应该是EDB,且lengh 字段全为0)。

同理SDP之后紧跟dllp包内容。

在 数据流中发送一个 SOS(SKP 有序集) 时,遵循以下流程:

-

在当前数据块(Data Block)的最后一个 dword(32 位字)发送一个 EDS Token(End of Data Stream 标记符号)。

-

紧接着发送一个 SOS,作为下一个有序集块(Ordered Set Block)。

-

立即在 SOS 后发送一个新的数据块(Data Block)。数据流将从这个数据块的第一个 Symbol 重新开始。

-

如果要插入多个 SOS,它们不能像早期 PCIe 代那样连续发送。每个 SOS 前必须先有一个以 EDS Token 结尾的数据块。

-

该数据块可以包含 TLP、DLLP 或 IDL 等内容

-

对于多lane情况链路中发送了IDL码,那么stp或sdp必须在lane0中出现。

Receiver Framing Requirements

收到 STP(Start of TLP)Token 时:

-

必须检查:

-

CRC 和奇偶校验(Frame Parity)字段;

-

注意:有 Framing Error 的 STP Token 不算作 TLP 的一部分(报错时要独立处理)。

-

-

接收到 TLP 的最后一个双字(DW)后:

-

紧随其后的 Symbol 是下一个要处理的 Token;

-

接收端必须检查它是否是一个 EDB(End of Data Block)Token,用于标记该 TLP 已被 nullified(无效化)。

-

-

可选检查项(实现可选):

-

如果 TLP 长度字段为 0,则为 Framing Error;

-

如果同一个 Symbol Time 内收到多个 STP Token,也应视为 Framing Error(若实现该检查)。

-

✅ 收到 EDB(End of Data Bad)Token 时:

-

接收器在检测到 第一个 EDB 符号时(或随后任何部分符号)必须立即通知链路层(Link Layer)。

-

如果 Token 中有任意 Symbol 不是合法的 EDB Symbol,判定为 Framing Error。

-

只有在一个 TLP 之后立即出现 EDB Token 是合法的,其他位置使用 EDB 都是 Framing Error。

✅ 收到 EDS(End of Stream)Token 作为数据块最后一个双字(DW)时:

-

接收器必须停止当前数据流处理。

-

接下来只允许收到以下三种 Ordered Set 中之一:

-

SKP

-

EIOS

-

EIEOS

否则为 Framing Error。

-

• 当接收到一个 IDL(空闲)token时:

— 下一个token可以在任意双字(DW)对齐的通道(Lane)上开始,前提是该通道在 IDL 令牌之后。对于 x4 或更窄的链路来说,这意味着下一个令牌只能在下一个符号时间(Symbol Time)的 Lane 0 上开始。而对于更宽的链路,例如 x16 链路,下一个令牌可以在当前符号时间的 Lane 0、4、8 或 12 上开始。

— 在同一个符号时间内,唯一可能出现在 IDL 令牌之后的令牌是另一个 IDL 或 EDS(端数据流)令牌。

• 在处理数据流期间,接收器将以下情况视为帧错误(Framing Errors):

— 一个有序集(Ordered Set)紧跟在 SDS(开始数据流)之后;

— 一个具有非法同步头(Sync Header,值为 11b 或 00b)的数据块(Block);这类错误可以选择性地在 Lane 错误状态寄存器中报告;

— 在任一通道上接收到一个有序集块(Ordered Set Block),但在前一个块中未收到 EDS 令牌;

— 一个数据块紧跟在前一个块中的 EDS 令牌之后;

— (可选)验证所有通道接收到的有序集是否一致。

Recovery from Framing Errors

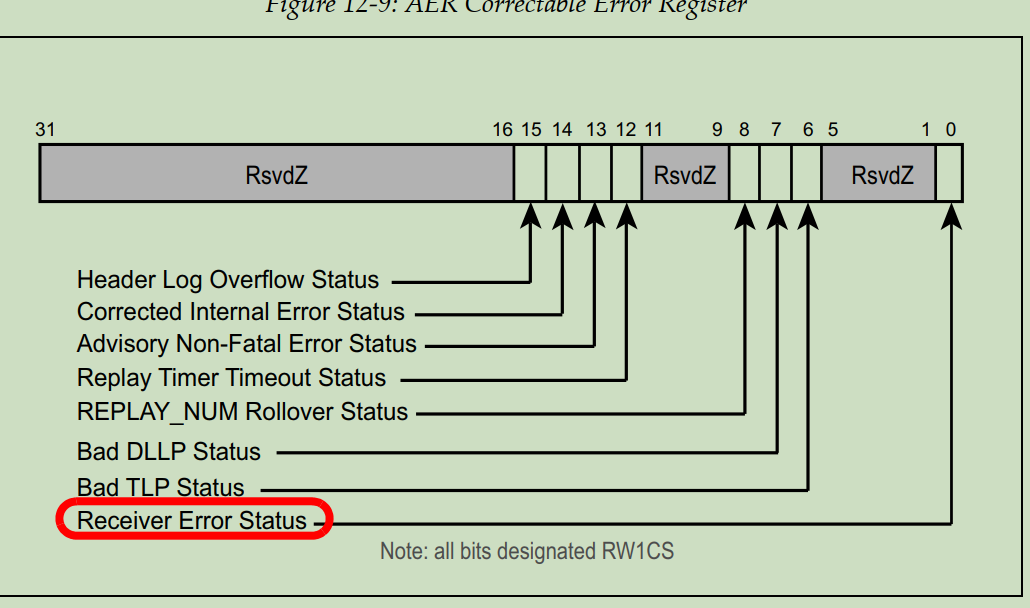

在AER中使能receiver error status;