扫描添加同名星球

免费查看所有收费合集

芯片SIPI设计星球

随着工艺尺寸的缩小、功能与性能的不断提升(包括高速接口),DIE(芯片)、PKG(封装)和PCB(印制电路板)的协同设计面临重大挑战,需满足系统级电气规格(如功耗、性能、面积、时序、PISI、IR压降、热管理、EMI/EMC)和BOM成本(如DIE、PKG、PCB成本)。

针对高速接口的DIE-PKG-PCB协同设计方法

A. 芯片层级协同设计优化

芯片层级的优化需兼顾功耗、性能、时序等系统需求,同时缩小芯片尺寸以降低成本。关键优化点包括:

Padring/IO环优化

优化IO架构、物理IO总线布局及多高速接口的IO分段,以改善PISI并缩小芯片尺寸。

电源供应优化与整合:减少电源数量,优化各电压域的PG焊盘(信号与电源比S2P)、去耦电容需求及PDN阻抗,以降低系统级BOM成本。

电源架构优化

电源架构在芯片和系统层级均至关重要,需制定芯片级电源管理策略(如内部/外部稳压、高低压监测、隔离电源、ADC/OSC等关键模拟IP的参考电压)。

封装与PCB层级的电源规划需与芯片电源域匹配,并通过PMIC优化满足SoC整体功耗需求。

多电压与多电源域划分策略,以支持不同应用场景的高低功耗模式。

分区/子系统与布局规划

基于数据驱动的子系统划分与架构设计,优化时序收敛并管理设计复杂度。

采用全邻接设计以控制复杂SoC的子系统尺寸。

子系统与硬核(SRAM、模拟IP)的摆放需满足时序与IR压降要求。

基于功耗与时序的布局规划。

布局与布线

优化时序、功耗及可制造性(DFM)。

Padring优化是协同设计的关键,需结合封装优化以满足高速接口的时序要求(如上升/下降时间、占空比、建立/保持时间、眼图等)。

B. 封装层级协同设计优化

封装层级的优化需选择低成本封装(如引线键合BGA、倒装芯片、WLCSP等),并考虑以下参数:

I/O信号焊球数量:根据应用需求确定信号、电源与地焊球数量,从而选择封装类型与尺寸。

封装类型选择:引线键合BGA成本低但电热性能较差,倒装芯片(铜柱或焊球)性能更优但成本较高。封装尺寸、焊球间距和层数需满足电热规格与成本目标。

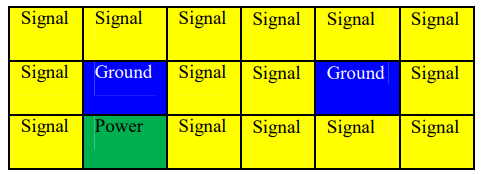

焊球分配策略:信号、电源与地的焊球分配需最小化布线层数,缩短走线长度以降低寄生RLC参数,从而控制电源噪声与PDN阻抗。地焊球需邻近信号/电源焊球以减少噪声耦合与回流路径(如表1所示)。

时钟-数据偏移:通过控制RX/TX信号走线长度差来优化时序偏移。

传输线阻抗匹配:封装与PCB的走线阻抗需符合目标要求(如50Ω)。

关键信号屏蔽:通过地参考层或相邻地平面减少电感与电容耦合。

表1 优化电源与地焊球分配的构造式策略

C. PCB层级协同设计优化

PCB层级的优化需在控制成本的同时满足电气规格,具体包括:

最小化布线层数。

优化去耦电容布局:针对高低频噪声优化,并满足DIE+PKG+PCB的PDN阻抗要求。

缩短外部组件与高速接口的走线长度:减少寄生RLC参数与负载,并控制传输线阻抗(如50Ω)。

PMIC优化:根据电源管理架构提供系统级电源。

信号分层布线:同类信号(如TX、RX)集中布线以减少时序偏移和上升/下降时间,同时降低PCB成本。

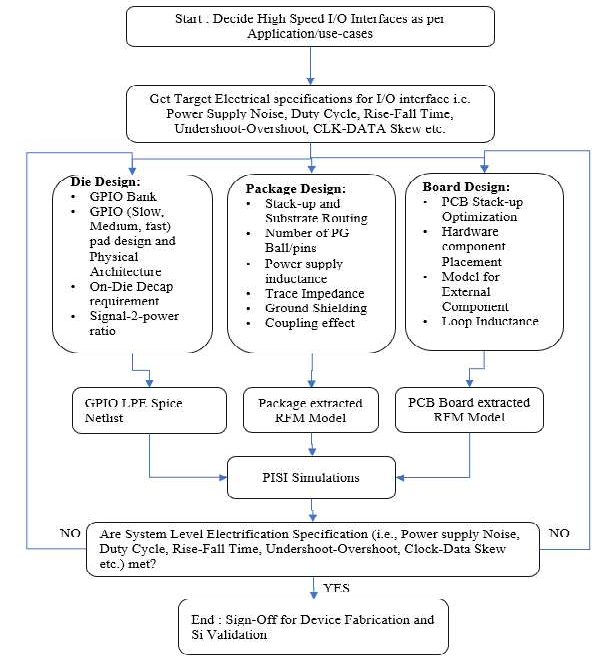

DIE-PKG-PCB协同设计流程与算法

图1 展示了所提方法的流程与算法,通过并行优化DIE-PKG-PCB以满足高速接口的电气规格并控制系统成本。

图1 设计流程方法

电气规格驱动关键参数,如电源噪声、上升/下降时间、占空比、时钟-数据偏移、PDN阻抗。电源噪声决定封装设计的PDN阻抗与电感量,从而影响PG焊球数量。IO接口的上升/下降时间与频率驱动IO焊盘架构设计。时序要求通过走线阻抗与延迟参数(R、L、C)实现。

复杂汽车SoC的协同设计实现与仿真结果

所提方法应用于一款复杂汽车SoC,该芯片包含数百万数字门电路、多高速接口、复杂电源架构(3个核心电压域与5个IO电压域),采用引线键合BGA封装。

芯片层级优化:Padring的S2P比为4:1,均匀分布PG焊盘,集成5个高速接口(共66个GPIO焊盘),去耦电容数量最小化,电源噪声低于15%。通过控制RX/TX走线长度差优化时钟-数据偏移。

封装层级优化:采用4层低成本引线键合BGA,通过表1策略分配焊球,将PCB布线层数降至2层。

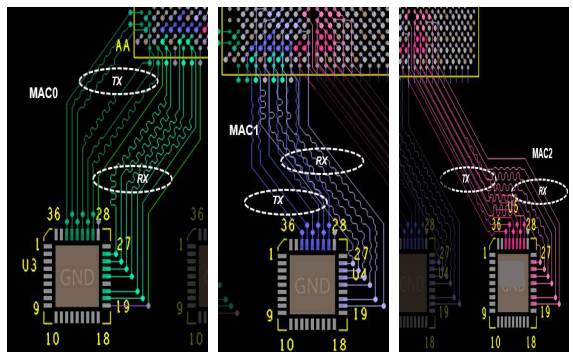

PCB层级优化:2层布线实现高速接口信号传输(如图3所示)。

图3 器件和封装球之间的PCB级走线,用于多个高速接口,显示为RX, TX信号实现的2层出线

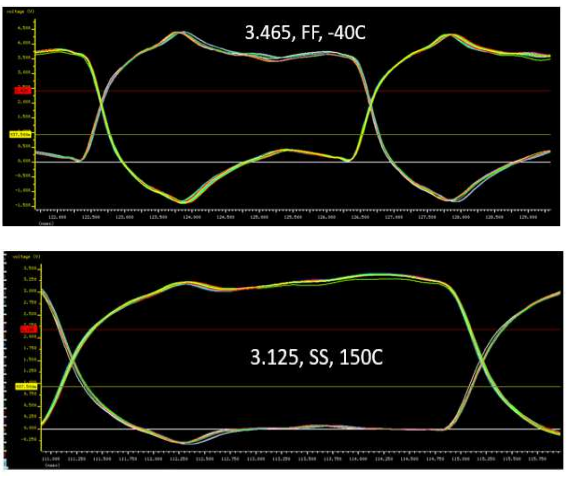

图4 展示了PISI仿真结果(使用工业级工具),包括上升/下降时间、过冲(OS)、下冲(US)、占空比及时钟/数据信号眼图(覆盖最差PVT条件:3.125V、SS、150℃与最佳条件:3.465V、FF、-40℃)。

图4 眼图为CLK,数据信号采用PISI仿真结果,波形显示上升/下降。

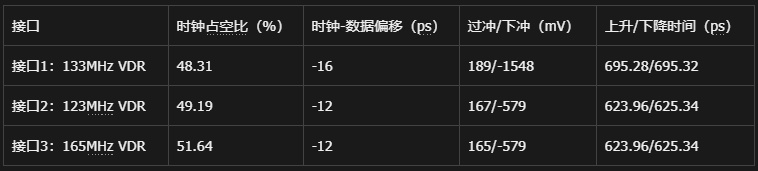

表2 列出了通过协同设计与系统级PISI仿真实现的时序参数:

静态IR压降分析(图5)显示DIE+PKG+PCB的最大压降为50mV(符合规格)。系统级热仿真验证结-环境热阻(Theta-JA)为8℃/W。

图5 redhawk DIE+PKG进行静态IRdrop分析结果

结论与总结

所提方法通过协同优化实现了:

芯片:减少IO电源域数量与PG焊盘,整合相同电压接口以缩小芯片尺寸。

封装:最小化布线层数与封装尺寸,优化焊球分配以降低封装成本。

PCB:2层布线满足高速接口需求并降低成本。

该方法为SoC设计者提供了系统级视角,兼顾电气规格与成本优化,适用于复杂汽车SoC设计。

以下广告时间

G

O

芯片SIPI设计课程视频培训

课程均可提供培训原视频

添加老师咨询

﹀

﹀

﹀

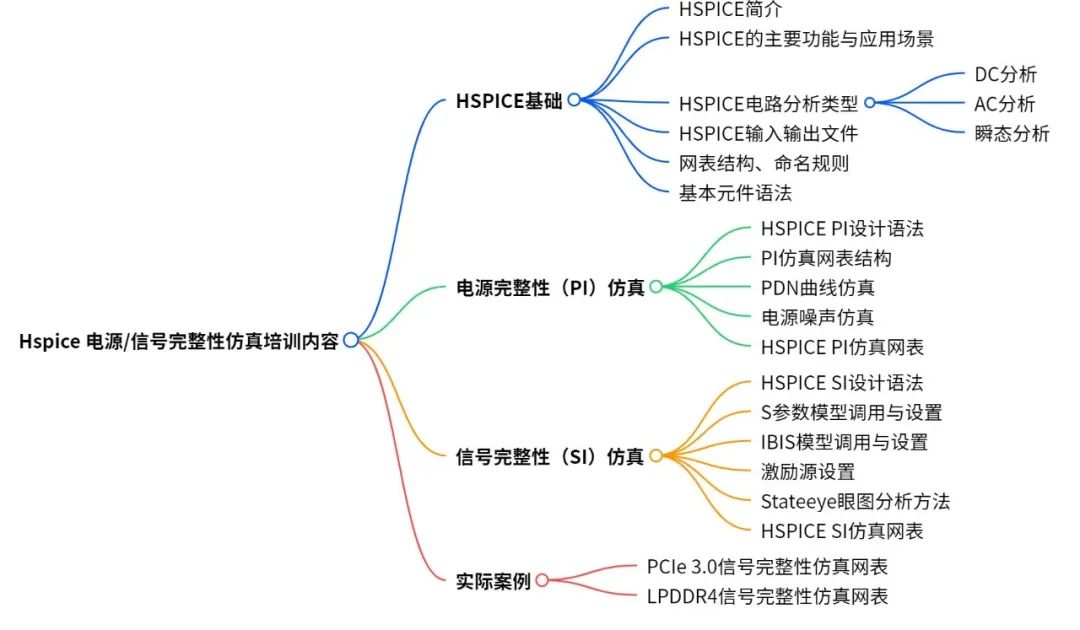

Hspice电源/信号完整性仿真培训

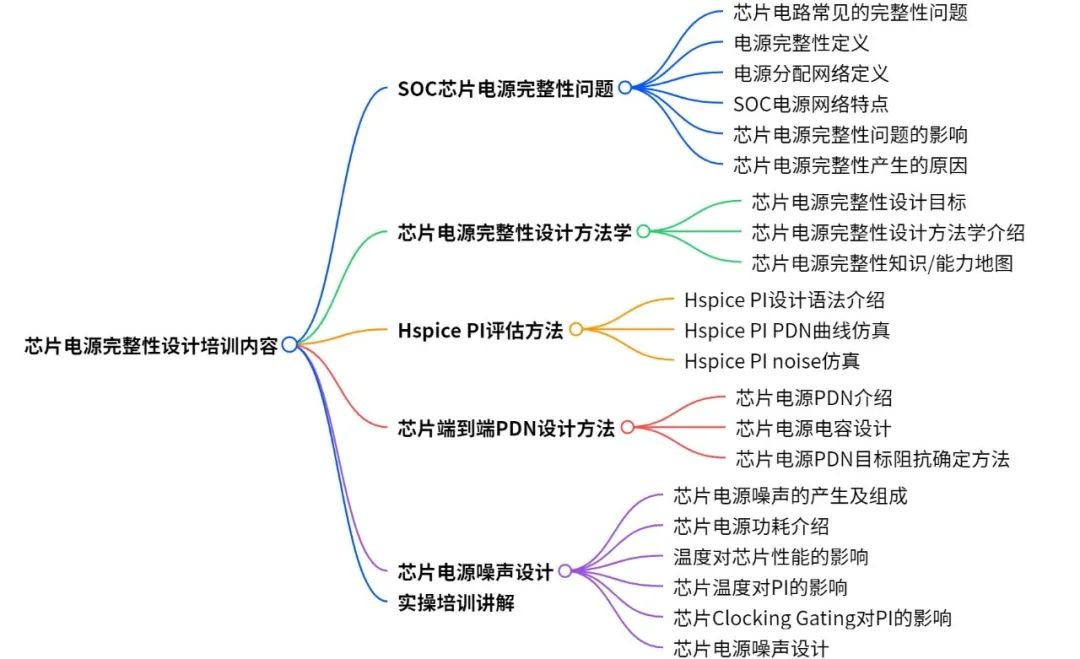

芯片电源完整性设计培训

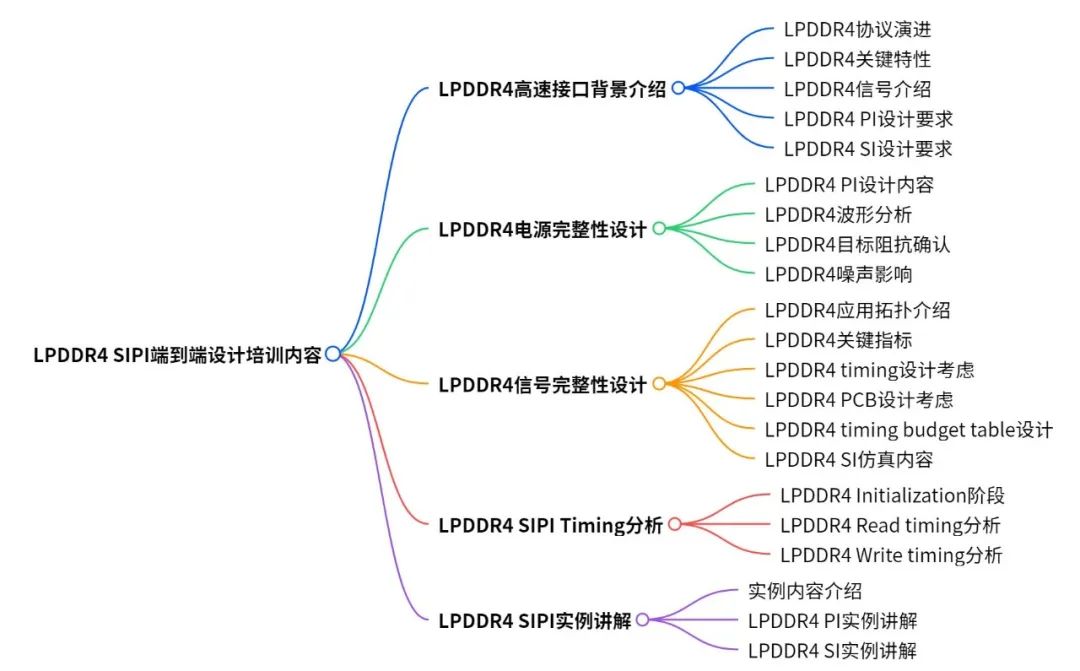

LPDDR4 SIPI端到端设计培训

、地图打印(webprinting)等服务)

——日期类和const成员函数)